## Single silicon vacancy-oxygen complex defect and variable retention time phenomenon in dynamic random access memories

## T. Umeda<sup>a)</sup>

Graduate School of Library, Information and Media Studies, University of Tsukuba, Tsukuba 305-8550, Japan

K. Okonogi, K. Ohyu, S. Tsukada, and K. Hamada *Elpida Memory, Inc., Sagamihara* 229-1198, *Japan*

## S. Fujieda and Y. Mochizuki

System Devices Research Laboratories, NEC Corporation, Sagamihara 229-1198, Japan

(Received 27 February 2006; accepted 4 May 2006; published online 22 June 2006)

The variable retention time phenomenon has recently been highlighted as an important issue in dynamic random access memory (DRAM) technology. Based on electrically detected magnetic resonance and simulation studies, we suggest that a single Si vacancy-oxygen complex defect is responsible for this phenomenon, when the defect is embedded in the near surface drain-gate boundary of a DRAM cell. © 2006 American Institute of Physics. [DOI: 10.1063/1.2213966]

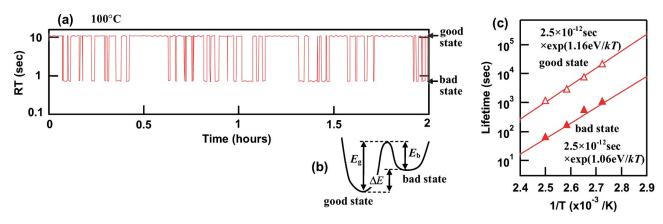

In 1992 Restle et al. reported the two-level variable retention time (VRT) phenomenon of dynamic random access memory (DRAM), which was observed universally in 64 Kbit–16 Mbit DRAMs of various manufacturers. We also observed this phenomenon in a 256 Mbit DRAM cell, as shown in Fig. 1(a). The two-level VRT is characterized by two reversible states (deemed "good" and "bad") that exhibit two discrete data retention times (RTs). It was recently demonstrated that the junction leakage current (JLC) of a VRT bit reversibly changes between low and high levels, causing the VRT phenomenon.<sup>2</sup> Similar two-level "telegraph" phenomena were also observed as random telegraph noise in the channel current of a small Si field effect transistor<sup>3</sup> and in the leakage current of an ultrathin SiO<sub>2</sub> film. This noise originates from the interaction between a single defect and the carriers.<sup>3,4</sup> Likewise, the VRT phenomenon is believed to be related to a single "bistable" defect (VRT defect); 1,2 however, its microscopic entity is still unclear. Since the VRT has a drastic impact on a DRAM's performance and reliability, <sup>2,5,6</sup> this is a highly important issue.

In this letter, we suggest that Si vacancy-oxygen (VO) complexes are the most likely source of the VRT defect. We detected such complexes in DRAM cells by means of electrically detected magnetic resonance (EDMR). The location, electronic levels, and bistable nature of those complexes are discussed in conjunction with the basic features of the VRT.

First, we found that the characteristic thermal activations of the VRT in old and current DRAMs are similar. Restle *et al.*<sup>1</sup> established that VRT can be described using a bistable energy diagram with two energy barriers,  $E_g$  and  $E_b$  [Fig. 1(b)]. The average lifetime for a good (bad) state is in proportion to  $\exp[E_{g(b)}/kT]$ , where k is the Boltzmann constant and T is temperature. For our VRT bits, as shown in the Arrhenius plot in Fig. 1(c),  $E_g$  and  $E_b$  were found to be approximately 1.16 and 1.06 ( $\pm 0.06$ ) eV, respectively, which are close to Restle's values ( $E_g$ =0.90–1.04 eV,  $E_b$ =0.84–1.08 eV, and generally  $E_g$ > $E_b$ ). We also found that their activation energies were between 0.7 and 1.4 eV; how-

ever, most cases exhibited a barrier of approximately 1 eV and  $E_g > E_b$ . Therefore, the nature of the VRT defect is apparently unchanged in current DRAMs. This defect must be located in the Si depletion layer since it generates the JLC.

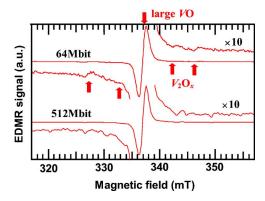

To investigate this defect, we performed EDMR measurements on the JLC in 10 000 DRAM cells with 64 or 512 Mbit technologies (gate length=0.25 and 0.11  $\mu$ m and junction area  $\approx 2500$  and 300  $\mu$ m<sup>2</sup>, respectively). The EDMR setup and measurement conditions used here were basically the same as those previously reported. <sup>7,8</sup> Figure 2 shows typical EDMR spectra for the two samples when the reverse bias  $(V_R)$  was applied to their pn junctions (the  $n^+$ -drain to the p-well). Two types of defects were observed in the 64 Mbit sample; they were assigned to large VO complexes  $(V_6 \text{ or larger})$  or  $V_2O$  and  $V_2O_2$   $(V_2O_x)$  based on a previous detailed study. The 512 Mbit sample clearly exhibited a large VO signal, but the  $V_2O_x$  signal was unclear due to noise. Nevertheless, we deduced that both types of defects were present in every DRAM, because they were formed by ion implantation in the drain  $(n^+)$  region, which is a fundamental process for DRAM technology. The defects possess two or more Si dangling bonds (DBs), which generate electronic levels  $E_t$  in the gap; for the  $V_2O_x$  type (with two DBs, electron spin S=1), two (+|0) levels lie at  $E_V$  (valence band top)+0.3-0.4 eV. These levels are similar to those of the well-known  $P_b$  center (DB at Si-SiO<sub>2</sub> interface). We thus speculate that  $E_t$  exists at similar positions for the large VO defects because they also have DBs. Their EDMR signal intensities were sensitive to the gate voltage, indicating that they were located in the near-surface drain region close to the gate.<sup>7</sup> These complexes are the likely source of the VRT defect.

The JLC due to the defect *J* can be calculated using the well-known Shockley-Read-Hall formula, <sup>10</sup>

$$J = C_n C_p v_{th} n_i / [C_n \exp(-E/kT) + C_p \exp(E/kT)],$$

where  $C_{n(p)}$  is the electron (hole) capture cross-section,  $v_{th}$  is the carrier thermal velocity  $[=(3kT/m^*)^{1/2}$ ; we used the effective mass  $(m^*=0.25m_0)$  for Si (Ref. 11)],  $n_i$  is the intrinsic carrier concentration of Si, and E is the difference between

a) Electronic mail: umeda@slis.tsukuba.ac.jp

FIG. 1. (Color online) (a) Two-level VRT phenomenon observed in 256 Mbit DRAM cell. (b) Bistable energy diagram for VRT (Ref. 1). (c) Thermal activation of reversible change between good and bad states for 256 Mbit DRAM cell.

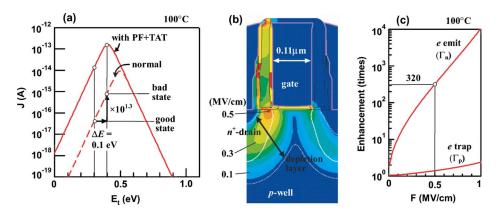

the intrinsic Fermi level and the defect level  $(=E_i-E_t)$ . We simulated J vs  $E_t$  for a typical defect level, <sup>12</sup> as shown in Fig. 3(a) (the "normal" curve). The good and bad states correspond to energetically lower and higher defect levels, which are separated by  $\Delta E (=E_g-E_b\approx 0.1 \text{ eV})$ , as assumed in Fig. 1(b). The simulated change in J was  $10^{1.3}$ , which is comparable to the observed change in RT [see Fig. 1(a)].

However, the simulated JLC from the bad state was 1/100 or less of the actual current level (100 fA or more). This inconsistency can be reasonably accounted for by the presence of a strong electric field (F) in the device. Using a standard numerical simulator, we simulated the electric field distribution in a 256/512 Mbit DRAM cell operating under normal charge retention. As shown in Fig. 3(b), the highest electric field (0.5 MV/cm) was observed at the boundary between the  $n^+$  drain and the gate, which coincides with the region where the VO complexes were embedded. With such a strong F, the (+|0) level of a DB can activate the Poole-Frenkel effect (PF). The trap assisted tunnel (TAT) effect can also work. Using previously reported formulas,  $^{11,13}$  we calculated the enhancements to the electron emission and trap rates from the (+|0) level,

$$E_{\rm PF} = (qF/\pi\varepsilon)^{1/2},$$

$$\Gamma_n = \exp(E_{\rm PF}/kT) + \int_{E_{\rm PF}/kT}^{(E_{\rm gap} - E_t)/kT} \\ \times \exp\{z - \alpha z^{3/2} [1 - (E_{\rm PF}/zkT)^{5/3}]\} dz,$$

FIG. 2. (Color online) Typical EDMR spectra measured for JLCs of 64 and 512 Mbit samples (80 nA at  $V_R$ =9.6 V and 55 nA at  $V_R$ =5.9 V, respectively) at room temperature with the magnetic field parallel to [011] axis.

$$\Gamma_p = 1 + \int_0^{E_t/kT} \exp\{z - \alpha [(E_{\text{gap}}/kT)^{3/2} - (E_{\text{gap}}/kT)^{3/2} - (E_{\text{gap}}/kT)^{3/2}]\} dz,$$

$$\alpha = 8\pi [2m^*(kT)^3]^{1/2}/3qhF,$$

where  $E_{\rm PF}$  is the potential-barrier reduction due to the PF effect, q is the electron charge, F is the applied electric field,  $\varepsilon$  is the dielectric constant of Si,  $\Gamma_n$  expresses the enhancement for electron emission due to PF (the first term) and TAT (the second term),  $\Gamma_p$  expresses the electron-trap enhancement by TAT,  $E_{\rm gap}$  is the band gap of Si, and h is Planck's constant. We estimated that the electron emission from the defect level is enhanced 320 times at 0.5 MV/cm, as shown in Fig. 3(c). Therefore, the previous simulation of J (the normal curve) should be revised to appear like the "with PF+TAT" curve in Fig. 3(a). As a result, we expect the JLC to be over 100 fA for the bad state, which is a reasonable level to account for the VRT.

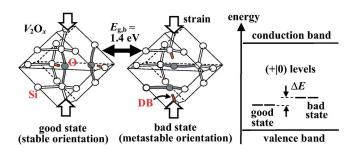

The VRT defect should be bistable with activation energies  $(E_g$  and  $E_b)$  of approximately 1 eV. We propose here a model of strain-induced bistability for the small VO complexes  $(V_2O_x)$ . They are formed as rare defects because their EDMR signal intensity was very small. This corresponds to previous findings that VRT bits appear with a small probability. For the case of  $V_2O_x$  under a strong lattice strain, one orientation becomes more stable than the other, as was demonstrated in electron paramagnetic resonance experiments under artificial strain.<sup>14</sup> Using convergent beam electron diffraction, we observed strain of over 100 MPa in the relevant devices.8 We deduced that the good and bad states correspond to two orientations, like those shown in Fig. 4. The reorientation of  $V_2O_x$  is similar to that of divacancy  $(V_2)$ , with an estimated activation barrier of  $\sim 1.4 \text{ eV}$ . This barrier is compatible with that observed for the VRT.

The above discussion implies that the impact of the  $V_2O_x$  complex on the VRT depends strongly on F and strain (namely,  $\Delta E$ ). This may explain (1) why the VRT exhibits a very wide variation, such that RT is changed by several percent to 1–2 orders of magnitude<sup>1,5</sup> (because the JLC varies in the above range depending on F and  $\Delta E$ ) and (2) why the VRT is affected by the packaging and thermal processes<sup>5,6</sup> (because they change the distribution of strain in a device).

FIG. 3. (Color online) (a) Simulated junction leakage current J from defect level  $E_r$ , assuming that electron and hole capture cross-sections ( $C_n$  and  $C_p$ , respectively, in cm<sup>2</sup>) are  $C_n = 1 \times 10^{-14}$ ,  $C_p = 1 \times 10^{-15}$  for "normal" curve,  $C_n = 320 \times 10^{-14}$ , and  $C_p = 1 \times 10^{-15}$  for "with PF+TAT" curve. Good (bad) state is set to  $E_V + 0.3$  (0.4) eV. (b) Simulated two-dimensional electric field distribution in 256/512 Mbit DRAM cell under normal charge retention operation. (c) Enhancement factors for electron emission and trap rates due to Poole-Frenkel effect (PF) and trap assisted tunneling effect (TAT).

The role of the large VO complexes on the VRT phenomenon is not clear at present. However, their DBs can interact with hydrogen atoms (H) and potentially cause H-related phenomena. Recent experiments suggested a correlation between H and the RT degradation observed at a relatively low  $T (\leq 250 \, ^{\circ}\text{C})$ . They also suggested that VRT is correlated with H. The VO complexes may be related to these H-related phenomena.

In summary, using EDMR, we observed that the VO complexes were present in all the DRAM cells we investigated. Numerical simulation showed that a single bistable VO defect located in the near surface gate-drain boundary can behave as a VRT defect.

FIG. 4. (Color online) Model for bistable  $V_2O_x$  defect under strain: (a) Atomic view and (b) energy-level view.

One of the authors (T.U.) thanks Professor Junichi Isoya (University of Tsukuba) for his valuable help in conducting the experiments.

<sup>1</sup>P. J. Restle, J. W. Park, and B. F. Lloyd, Tech. Dig. - Int. Electron Devices Meet. **1992**, 807.

<sup>2</sup>Y. Mori, K. Ohyu, K. Okonogi, and E. Yamada, Tech. Dig. - Int. Electron Devices Meet. **2005**, 41.

<sup>3</sup>M. J. Kirton and M. J. Uren, Appl. Phys. Lett. **48**, 1270 (1986); P. Restle and A. Gnudi, IBM J. Res. Dev. **34**, 227 (1990).

<sup>4</sup>M.-J. Chen and M.-P. Lu, Appl. Phys. Lett. **81**, 3488 (2002).

I. Kim, K. H. Yang, and W. S. Lee, Reliability Physics Symposium Proceedings, 2004, 42nd Annual (IEEE International, 2004), pp. 667–668.

M. Chang, J. Lin, C.-S. Lai, R.-D. Chang, S. N. Shih, M.-Y. Wang, and P.-I. Lee, IEEE Trans. Electron Devices 52, 484 (2005).

<sup>7</sup>T. Umeda, Y. Mochizuki, K. Okonogi, and K. Hamada, J. Appl. Phys. 94, 7105 (2003).

<sup>8</sup>T. Umeda, A. Toda, and Y. Mochizuki, Eur. Phys. J.: Appl. Phys. **27**, 13 (2004).

<sup>9</sup>S. Coffa and F. Priolo, *Properties of Crystalline Silicon* (INSPEC, London, 1999), edited by R. Hull, p. 748.

<sup>10</sup>S. M. Sze, *Physics of Semiconductor Devices* (Wiley, New York, 1981), Chap. 2.

<sup>11</sup>G. A. M. Hurkx, D. B. M. Klaassen, and M. P. G. Knuvers, IEEE Trans. Electron Devices 39, 331 (1992).

<sup>12</sup>B. G. Svensson, *Properties of Crystalline Silicon* (INSPEC, London, 1999), edited by R. Hull, p. 764.

<sup>13</sup>G. Vincent, A. Chantre, and D. Bois, J. Appl. Phys. **50**, 5484 (1979).

<sup>14</sup>G. D. Watkins and J. W. Corbett, Phys. Rev. **138**, A543 (1965).